UTK - Architektura komputera

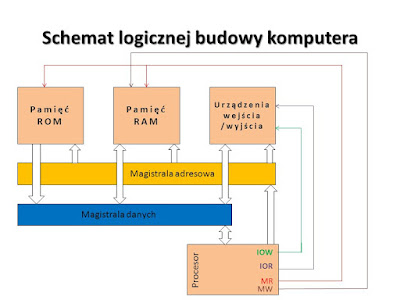

1. Architektura komputera określa połączone ze sobą 3 podstawowe elementy: procesor, pamięć i urządzenia wejścia-wyjścia.

Współpraca pomiędzy procesorem i urządzeniami I/O odbywa się przez szynę danych i szynę adresową. Procesor wysyła sygnały sterujące, które umożliwiają odczyt lub zapis z poszczególnych urządzeń.

Sygnały sterujące to:

5. Transmisja pomiędzy RAM i I/O lub po między innymi elementami systemu może odbywać się w dwóch trybach PIO i DMA.

2. Procesor jest głównym elementem komputera, który odpowiada za przetwarzanie danych.

- ALU - jednostka arytmetyczno-logiczna (tam realizowane są operacje na liczbach dwójkowych)

- CU - jednostka sterująca (pobiera dane z pamięci i dostarcza do ALU)

- zespół rejestrów (przechowuje się tam adresy wybranych miejsc w pamięci, a także dane i wyniki obliczeń)

3. Pamięć wewnętrzna składa się z:

- pamięci ROM (tylko do odczytu, przechowywane są informacje o konfiguracji sprzętowej oraz programy diagnostyczne)

- pamięci RAM (w niej przechowywane przetwarzane dane, programy iwyniki wykonania programów, po wyłączeniu zasilania wyniki są tracone)

4. Magistrala to zespół linii służący do przesyłania danych, adresów i sygnałów między CPU, RAM , ROM i urządzeniami wejścia-wyjścia. Mamy 4 rodzaje magistral systemowych:

- FSB - łączy procesor z kontrolerem pamięci

- DMI - łączy mostek północny i południowy

- QPI - dwukierunkowa magistrala (w Intelach zastąpiła FSB)

- Hyper Transport (w AMD) - występuje CPU z wbudowanym kontrolerem pamięci

Współpraca pomiędzy procesorem i urządzeniami I/O odbywa się przez szynę danych i szynę adresową. Procesor wysyła sygnały sterujące, które umożliwiają odczyt lub zapis z poszczególnych urządzeń.

Sygnały sterujące to:

- MR (odczyt pamięci)

- MW (zapis do pamięci)

- IOR (odczyt z urządzeń wejścia-wyjścia)

- IOW.(zapis do urządzeń wejścia-wyjścia)

Ze względu na ograniczoną do 16 liczbę przerwań sprzętowych zewnętrznych, są one często współdzielone przez kilka urządzeń systemowych, oprócz tych, które są wyszczególnione powyżej.

6. PIO - tryb, w którym CPU zajmuje się transmisją danych, czyli adresowaniem i nadzorem szyny danych

7. DMA - tryb, w którym CPU programuje kontroler DMA.

8. CPU odłącza się od magistrali, kiedy obciążenie procesora jest niskie. Procesor wcześniej programuje rejestry DMA, do których wpisuje adres początkowy, od którego nastąpi transmisja ilości danych, które będą transmitowane.